Publicado el 23 de Julio del 2019

1.107 visualizaciones desde el 23 de Julio del 2019

333,7 KB

16 paginas

Creado hace 5a (12/09/2018)

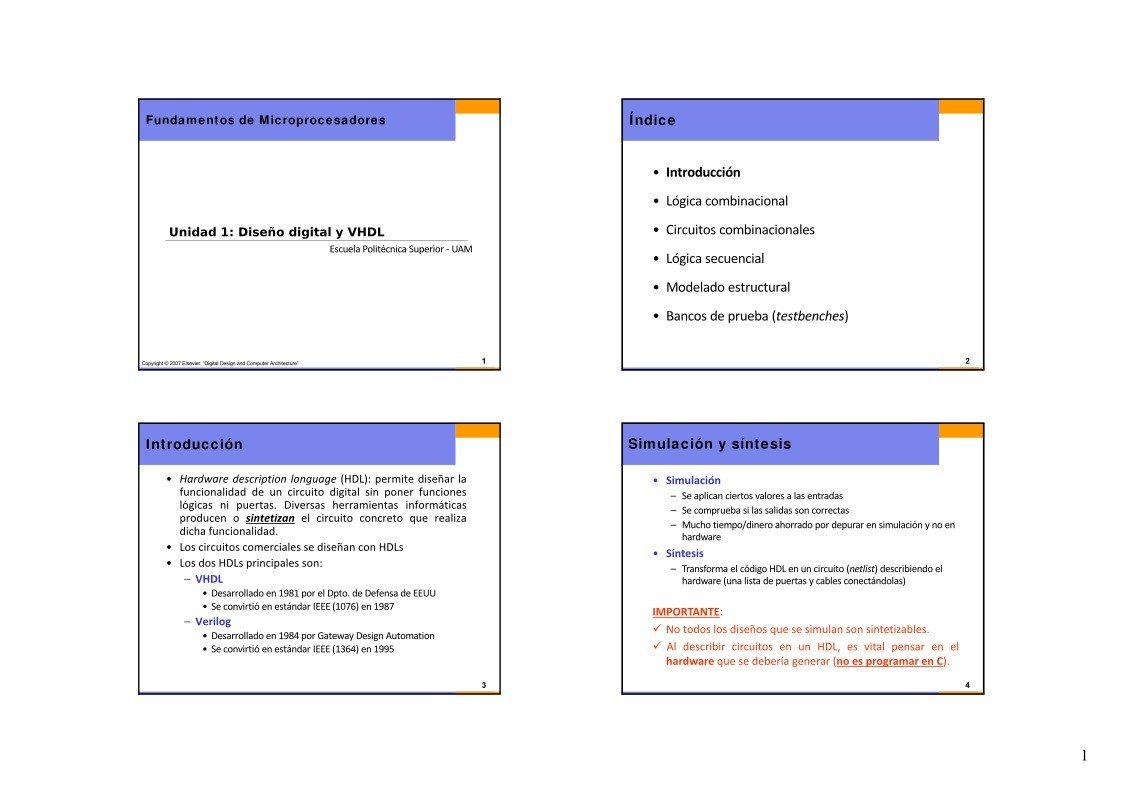

Fundamentos de Microprocesadores

Índice

Unidad 1: Diseño digital y VHDL

Escuela Politécnica Superior ‐ UAM

Copyright © 2007 Elsevier, “Digital Design and Computer Architecture”

Introducción

• Hardware description language (HDL): permite diseñar la

funcionalidad de un circuito digital sin poner funciones

lógicas ni puertas. Diversas herramientas informáticas

producen o sintetizan el circuito concreto que realiza

dicha funcionalidad.

• Los circuitos comerciales se diseñan con HDLs

• Los dos HDLs principales son:

– VHDL

– Verilog

• Desarrollado en 1981 por el Dpto. de Defensa de EEUU

• Se convirtió en estándar IEEE (1076) en 1987

• Desarrollado en 1984 por Gateway Design Automation

• Se convirtió en estándar IEEE (1364) en 1995

• Introducción

• Lógica combinacional

• Circuitos combinacionales

• Lógica secuencial

• Modelado estructural

• Bancos de prueba (testbenches)

Simulación y síntesis

• Simulación

– Se aplican ciertos valores a las entradas

– Se comprueba si las salidas son correctas

– Mucho tiempo/dinero ahorrado por depurar en simulación y no en

hardware

• Síntesis

– Transforma el código HDL en un circuito (netlist) describiendo el

hardware (una lista de puertas y cables conectándolas)

IMPORTANTE:

No todos los diseños que se simulan son sintetizables.

Al describir circuitos en un HDL, es vital pensar en el

hardware que se debería generar (no es programar en C).

2

4

1

3

1

Entidad - Arquitectura

PORTS: La conexión con el exterior

• La entidad se utiliza para hacer una descripción "caja negra" del

diseño, sólo se detalla su interfaz (los puertos de entrada y

salida “ports”)

Equivalente en C

float CalculaMedia(float a, float b) {

• Los contenidos del circuito se modelan dentro de la arquitectura

float CalculaMedia(float a, float b) {

float c;

c = (a+b) / 2;

return c;

float c;

c = (a+b) / 2;

return c;

}

}

• Una entidad puede tener varias arquitecturas

Ejemplo de código VHDL

library IEEE;

use IEEE.std_logic_1164.all; -- para usar std_logic

-- similar a declaración de .h

entity inversor is

entity inversor is

port (a : in std_logic;

port (a : in std_logic;

y : out std_logic);

y : out std_logic);

end inversor;

end inversor;

Inversor

y

a

architecture comportamental of inversor is

architecture comportamental of inversor is

begin

begin

y <= not a;

y <= not a;

end comportamental;

end comportamental;

-- asignación con flecha

-- asignación con flecha

S

A

C

E

T

O

L

B

B

I

I

D

A

D

T

N

E

I

A

R

U

T

C

E

T

U

Q

R

A

I

5

7

Tipo de Dato

Conjuntos de Valores que se les ha asignado un

nombre, de tal forma que un objeto (p.ej. una

Señal) de un determinado Tipo (p.ej. el tipo

std_logic) pueda tomar cualquier valor dentro

del conjunto de valores que define al Tipo

especificado.

std_logic

Valores ‘U’, ‘X’, ‘0’, ‘1’, ‘Z’,

‘W’, ‘L’, ‘H’, ‘‐’

(std_logic_1164)

std_logic_vector

(std_logic_1164)

Integer

(standard)

Boolean

(standard)

Vector de std_logic

Números enteros

Valores de cierto o falso

Nombre

Identificador

PORT

Modo

in = Entrada (sólo permite leer de)

out = Salida (sólo permite escribir en)

inout

•Puerto de Entrada (lectura) y Salida

(escritura)

•El valor leído (Entrada) es aquél que

llega al puerto, y no el valor que se le

asigna (Salida), en caso de existir.

Síntesis de código VHDL

VHDL:

architecture comportamental of ejemplo is

begin

y <= (not a and not b and not c) or (a and not b and not c) or

(a and not b and c);

end comportamental;

Síntesis:

b

c

a

un5_y

y

y

un8_y

6

8

2

Sintaxis VHDL

Sintaxis en VHDL: Identificadores

• No distingue mayúsculas de minúsculas (case insensitive)

– Ejemplo: reset y Reset son la misma señal.

– Recomendación: poner siempre las mismas mayúsculas para

facilitar la lectura y las búsquedas.

• Los nombres no pueden empezar por números

– Ejemplo: 2mux no es un nombre válido.

• Se ignoran los espacios, tabuladores, retornos de carro

• Comentarios:

‐‐ Desde un guión doble hasta el final de la línea.

Índice

• Introducción

• Lógica combinacional

• Circuitos combinacionales

• Lógica secuencial

• Modelado estructural

• Bancos de prueba (testbenches)

9

11

IDENTIFICADORES

Nombres o etiquetas que se usan para referirse a: Constantes, Señales,

Procesos, Entidades, etc.

Longitud (Número de Caracteres): Sin restricciones

Palabras reservadas por VHDL no pueden ser identificadores

En VHDL, un identificador en mayúsculas es igual que en minúsculas

Están formados por números, letras (mayúsculas o minúsculas) y guión

bajo “_” con las reglas especificadas en la tabla siguiente.

Reglas para especificar un identificador

Primer carácter debe ser siempre una letra mayúscula o minúscula

Segundo carácter no puede ser un guión bajo ( _ )

Dos guiones bajos consecutivos no son permitidos

Un identificador no puede utilizar símbolos especiales

Incorrecto

4Suma

S_4bits

Resta__4

Clear#8

Correcto

Suma4

S4_bits

Resta_4_

Clear_8

10

Tipo std_logic

• Los valores ‘0’ y ‘1’ del tipo bit se quedan cortos para modelar todos los

estados de una señal digital en la realidad

• El paquete IEEE.std_logic_1164 define el tipo std_logic, que representa

No inicializado, valor por defecto

Desconocido fuerte, indica cortocircuito

Salida de una puerta con nivel lógico bajo

Salida de una puerta con nivel lógico alto

Alta Impedancia

todos los posibles estados de una señal real:

U

X

0

1

Z

W Desconocido débil, terminación de bus

L

H

–

0 débil, resistencia de pull‐down

1 débil, resistencia de pull‐up

No importa, usado como comodín para síntesis

El tipo std_logic_vector define un array de bits de tipo std_logic.

12

3

Operadores bitwise

Asignación condicional: when … else

entity puertas is

port (a, b: in std_logic_vector(3 downto 0);

y1, y2, y3, y4, y5: out std_logic_vector(3 downto 0));

end puertas;

architecture comport of puertas is

begin

-- Pueden actuar sobre bits

-- o sobre buses

y1 <= a and b; -- AND

y2 <= a or b; -- OR

y3 <= a xor b; -- XOR

y4 <= a nand b; -- NAND

y5 <= a nor b; -- NOR

end comport;

Asignación condicional: with … select

entity deco2a4 is

port(a : in std_logic_vector(1 downto 0);

y : out std_logic_vector(3 downto 0));

end deco2a4;

architecture comport of deco2a4 is

begin

with a select

y <= “0001” when “00”,

“0010” when “01”,

“0100” when “10”,

“1000” when others;

end comport;

-- último caso, siempre

-- conviene incluirlo

P

13

15

entity mux2a1_4bits is

port(d0,d1 : in std_logic_vector(3 downto 0);

s : in std_logic;

y : out std_logic_vector(3 downto 0));

end mux2a1_4bits;

architecture comport of mux2a1_4bits is

begin

y <= d0 when s = ‘0’ else d1;

end comport;

P

14

Señales internas

architecture comport of fulladder is

signal p, g : std_logic; -- La declaración de señales internas

-- se pone entre architecture y begin

s

cout

16

4

begin

p <= a xor b;

g <= a and b;

s <= p xor cin;

cout <= g or (p and cin);

end comport;

cin

a

b

g

s

p

un1_cout

cout

Concurrencia

architecture comport of fulladder is

signal p, g : std_logic;

begin

p <= a xor b;

g <= a and b;

s <= p xor cin;

cout <= g or (p and cin);

-- No importa el orden de las

-- líneas, todo el hardware

-- “existe” a la vez

end comport;

-------------------------------------------------------

architecture comport of fulladder is

signal p, g : std_logic;

begin

cout <= g or (p and cin); -- Es el mismo circuito, no

s <= p xor cin;

p <= a xor b;

g <= a and b;

-- importa que p se asigne en

-- una línea posterior porque

-- el hardware es concurrente

end comport;

Formatos de números y bits

Formato

‘1’

“101”

X“AF”

1

-2

1.5

Nº bits

1

>1

>1

Depende

Depende

Depende

Memoria

1

101

Base

Binario

Binario

Hexadecimal 10101111

0…00001

Decimal

1…11110 (C2)

Decimal

Decimal

IEEE-754

Los valores de las señales se asignan con una “flecha”:

a_bit <= ‘1’;

a_bus <= “101”;

a_int <= 1;

Precedencia de operadores

• Orden en que se resuelven los operadores si no hay paréntesis

• Recomendación: usar paréntesis

Primero

Último

Operación

NOT

mult div módulo

suma

resta

Operador

not

* / %

+ -

< <= > >= comparar

= /=

and nand

xor xnor

or nor

igual

AND NAND

XOR XNOR

OR NOR

distinto

17

19

Manipulación de bits

signal a : std_logic_vector(3 downto 0);

signal b : std_logic_vector(0 to 3);

...

a <= “0101”;

b <= “0101”;

-- es equivalente a:

a(3) <= ‘0’; a(2) <= ‘1’; a(1) <= ‘0’;

b(2) <= ‘0’; b(1) <= ‘1’;

b(3) <= ‘1’;

a(0) <= ‘1’;

b(0) <= ‘0’;

a

b

Posición

Valor

Posición

Valor

3

0

0

0

2

1

1

1

1

0

2

0

0

1

3

1

18

20

5

Manipulación de bits

Manipulación de bits

signal y : std_logic_vector(7 downto 0);

signal a, b : std_logic_vector(3 downto 0);

...

-- el operador & en VHDL significa concatenar

y <= a & b(3) & ‘0’ & b(2 downto 1);

-- es equivalente a:

y(7) <= a(3); y(6) <= a(2); y(5) <= a(1);

y(4) <= a(0);

y(3) <= b(3); y(2) <= ‘0’;

y(1) <= b(2);

y(0) <= b(1);

a

y

3

7

2

6

1

5

0

4

3

2

1

0

b

0

2

3

1

0

21

Manipulación de bits

signal y : std_logic_vector(7 downto 0);

signal a, b : std_logic_vector(3 downto 0);

...

-- en VHDL se permite hacer asignaciones por índice en

-- lugar de orden (izquierda a derecha) bit a bit (aggregates)

y <= (3 downto 2 => a(2), 4 => b(1), 5 => ‘1’,

others => '0');

-- others es “resto de bits”

-- es equivalente a:

y(7) <= ‘0’; y(6) <= ‘0’; y(5) <= ‘1’; y(4) <= b(1);

y(3) <= a(2); y(2) <= a(2); y(1) <= ‘0’; y(0) <= ‘0’;

-- muy utilizado para la inicialización de buses:

y <= (others => ‘0’); -- poner todos los bits a ‘0’

P

23

signal y : std_logic_vector(7 downto 0);

signal a, b : std_logic_vector(3 downto 0);

...

-- Se pueden hacer todo tipo de agrupaciones parciales

-- siempre que coincidan el número de bits

y(7 downto 4) <= a;

y(3) <= b(3);

y(2) <= ‘0’;

y(1 downto 0) <= b(2 downto 1);

-- es el mismo resultado para la “señal y” que en la

-- transparencia anterior

y <= a & b(3) & ‘0’ & b(2 downto 1);

Z: alta impedancia

VHDL:

signal y, a: std_logic_vector(3 downto 0);

signal en : std_logic;

...

y <= (others => ‘

Crear cuenta

Crear cuenta

Comentarios de: Fundamentos de Microprocesadores (0)

No hay comentarios