Manual de Verilog

ver 0.4

Jorge Chávez

Marzo 1999

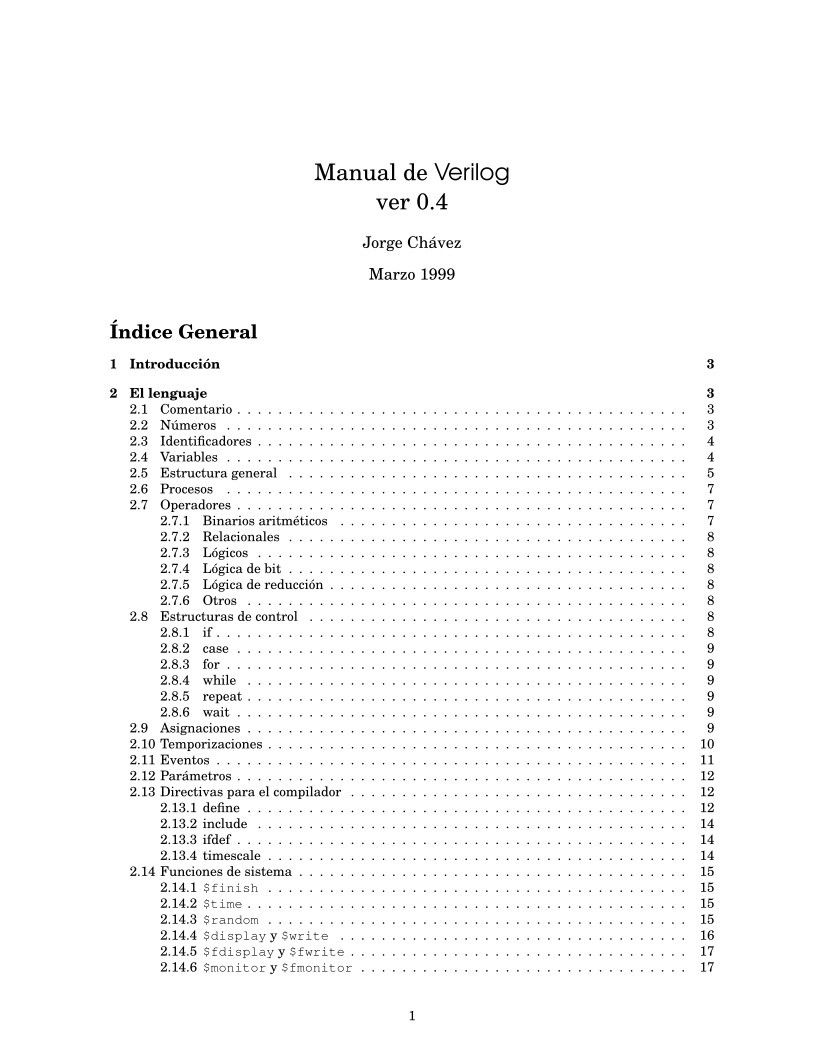

Índice General

1 Introducci ón

3

2 El lenguaje

2.8 Estructuras de control

3

3

2.1 Comentario . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 N úmeros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

4

2.3 Identificadores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

2.4 Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.5 Estructura general

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

2.6 Procesos

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

2.7 Operadores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Binarios aritméticos

7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.7.2 Relacionales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.3 Lógicos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.7.4 Lógica de bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.7.5 Lógica de reducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

8

2.7.6 Otros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.8.1 if . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.8.2 case . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.8.3 for . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.8.4 while . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.8.5 repeat . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.8.6 wait . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 Asignaciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.10 Temporizaciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.11 Eventos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.12 Parámetros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.13 Directivas para el compilador . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.13.1 define . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.13.2 include . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.13.3 ifdef . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.13.4 timescale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.14 Funciones de sistema . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.14.1 $finish . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.14.2 $time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.14.3 $random . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.14.4 $display y $write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.14.5 $fdisplay y $fwrite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.14.6 $monitor y $fmonitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1

ManualdeVerilog ,ver0.4

2

2.14.7 $dumpfile y $dumpvars . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.14.8 $readmemb y $readmemh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.15 funciones y tareas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3 Sintetizabilidad

4 M áquinas de estado

21

24

5 Ejemplos

26

5.1 De-Multiplexor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.2 Multiplexor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.3 Registro de desplazamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.4 Contador . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.5 Acceso bidireccional . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.6 Memorias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

ManualdeVerilog ,ver0.4

3

En este documento no se pretende describir exhaustivamente todas y cada una de las fun-

cionalidades de Verilog , sino dar una visión superficial sobre el lenguaje y de las difer-

entes descripciones que se pueden realizar de un sistema. El autor agradece cualquier

sugerencia o comentario sobre cualquiera de los aspectos de este documento:

Jorge Ch ávez

[email protected]

1 Introducci ón

Verilog es un lenguaje para la descripción de sistemas digitales (HDL: Hardware Description Lan-

guage). Los sistemas pueden ser descritos:

• Nivel estructural empleando elementos de librería o bien elementos previamente creados,

se realiza la interconexión de unos con otros. Sería similar a una captura esquemática donde

la función del dise ñador es instanciar bloques y conectarlos entre sí.

• Nivel de comportamiento el dise ñador describe la transferencia de información entre reg-

istros (nivel RTL: Register Transfer Level).

Estos dos niveles de descripción pueden mezclarse, dando lugar a los denominados dise ños mixtos1.

Existen multitud de lenguajes HDL en el mercado (de hecho inicialmente cada fabricante disponía

de su propio lenguaje), sin embargo la necesidad de unificación ha hecho que en la actualidad sólo

existan dos grandes lenguajes: VHDL y Verilog . Ambos están acogidos a estándares IEEE (VHDL

en 1987 y Verilog en 1995). Existen defensores y detractores de cada uno de ellos. Con carácter

general se dice que es más fácil aprender Verilog al ser un lenguaje más compacto2.

Verilog nació en 1985 como un lenguaje propietario de una compa ñía (Cadence Design System),

pero en 1990 se formó OVI (Open Verilog International) haciendo dicho lenguaje de dominio p úblico,

permitiendo a otras empresas que pudieran emplear Verilog como lenguaje, con objeto de aumentar

la difusión de dicho lenguaje.

2 El lenguaje

Uno de los aspectos que salta a la vista al contemplar un código Verilog es su similitud con el

lenguaje C. Una de las mayores diferencias que presenta este lenguaje es que permite modelar

sistemas digitales reales, que funcionan de forma paralela a diferencia de la ejecución secuencial,

típica de un sistema computacional.

2.1 Comentario

Existen dos alternativas: desde los caracteres “//” hasta el final de la línea es considerado comen-

tario. Otra alternativa es la zona comprendida entre “/*” y “*/”.

2.2 N úmeros

La expresión general de una cantidad es:

tama ño base n úmero

Donde:

1Seg ún el contexto, un dise ño mixto también podría ser aquel que mezcla analógico con digital

2un mismo dise ño ocupa menos líneas de código

ManualdeVerilog ,ver0.4

4

• tama ño es el n úmero de bits (expresado en decimal) de la cantidad que viene a continuación.

Es opcional.

• base indica la base en la que se va a expresar número. Es opcional, si no se indica es decimal.

base binaria

base decimal

’b

’d

’h base hexadecimal

’o

base octal

• n úmero es la cantidad. Para facilitar la lectura se pueden colocar “_”. Además de las cifras

permitidas en cada base (0-9 y A-F), se pueden emplear en el caso de base binaria:

x

z

para indicar que el valor de un bit es desconocido

para indicar que el valor de un bit es alta-impedancia

Ejemplos:

187

8’h0a

3’b1

’o73

2’b1x

n úmero decimal

n úmero hexadecimal de 8 bits

n úmero binario de 3 bits

n úmero octal

n úmero binario de dos bits cuyo bit menos

significativo es desconocido

n úmero binario de 4 bits en alta impedancia

n úmero binario de 4 bits complemento a 2 de 10 (1110)

4’bz

-4’b10

’b1000 0001 n úmero binario de 8 bits

2.3 Identificadores

Un identificador está formado por una letra o “_” seguido de letras, n úmeros y los caracteres “$” o

“_”. Se distingue entre may úsculas y min úsculas.

2.4 Variables

Existen 2 tipos fundamentales de variables:

• reg es un registro y permite almacenar un valor

• wire es una red que permite la conexión

Por defecto dichas variables son de un único bit, pero pueden declararse variables con un mayor

n úmero de bits:

tipo [ msb :

lsb ] varname ;

Ejemplo:

reg [5:0] C; // Es un registro de 6 bits, siendo C[0] el bit menos significa-

tivo.

También es posible también definir memorias, así por ejemplo:

reg [7:0] mem [0:1023]; // Es la declaración de una memoria de 1024 bytes.

Además de estos tipos existen otros tipos de datos más abstractos como: integer (registro de 32

bits), real (registro capaz de almacenar un n úmero en coma flotante) o time (registro unsigned de

64 bits).

ManualdeVerilog ,ver0.4

5

2.5 Estructura general

En Verilog un sistema digital está compuesto por la interconexión de un conjunto de m ódulos.

module <nombre del modulo> ( <señales> );

<declaraciones de señales>

<funcionalidad del módulo>

endmodule

Algunos aspectos a recordar son:

• Cada módulo dispone de una serie de entradas y salidas a través de las que se interconecta

con otros módulos, aunque puede no tener entradas ni salidas.

• No existen variables globales.

• Fuera de los módulos sólo puede haber directivas de compilador, que afectan al fichero a partir

del punto en el que aparecen.

• A pesar de que se pueden realizar varias

Crear cuenta

Crear cuenta

Comentarios de: Manual de Verilog (0)

No hay comentarios