¡Por supuesto, Antonio! Entenderé y explicaré cada una de las partes del ejercicio:

Pregunta 1:

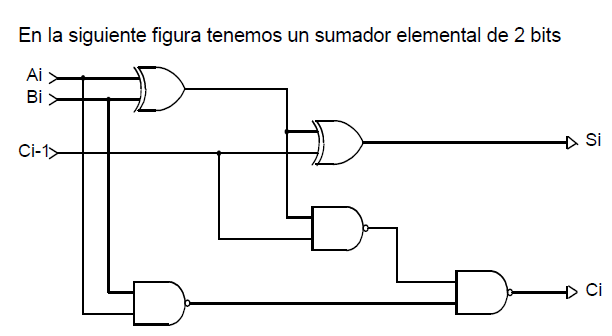

Si cada puerta tiene un retardo de 3 ns, necesitamos considerar cuántos niveles de puertas hay en la ruta crítica. En la figura que proporcionaste, el valor Si se obtiene a través de una serie de puertas AND y OR, y el valor Ci se obtiene a través de una serie de puertas XOR.

Para el valor Si:

- Las puertas AND tienen un retardo total de 3 ns (3 ns por nivel de puerta).

- Las puertas OR tienen un retardo total de 3 ns.

Para el valor Ci:

- Las puertas XOR tienen un retardo total de 3 ns.

Por lo tanto, el retardo total para obtener los valores Si y Ci será de 3 ns para cada uno.

Pregunta 2:

Para construir un sumador de 4 bits que sume dos números de cuatro bits con acarreo inicial, puedes utilizar cuatro sumadores de 1 bit y un sumador de 4 bits que sume los acarreos generados por los sumadores individuales. Aquí tienes un dibujo aproximado:

Donde:

- A y B son los bits de entrada.

- Si1, Si2, Si3 y Si4 son los sumandos intermedios.

- Ci1, Ci2, Ci3 son los acarreos intermedios.

- Co es el acarreo final.

Pregunta 3:

Dado que cada puerta tiene un retardo de 3 ns, necesitamos considerar cuántos niveles de puertas hay en la ruta crítica para el sumador de 4 bits. En este caso, el retardo total sería:

- Sumandos intermedios (Si1, Si2, Si3, Si4): 3 ns por nivel de puerta.

- Acarreos intermedios (Ci1, Ci2, Ci3): 3 ns por nivel de puerta.

- Acarreo final (Co): 3 ns por nivel de puerta.

Por lo tanto, el retardo total para obtener el resultado final y el acarreo final sería de 3 ns por nivel de puerta.

Recuerda que estas explicaciones son aproximadas y consideran que todas las puertas tienen el mismo retardo. En implementaciones reales, las diferencias de retardo pueden afectar los resultados.