Publicado el 14 de Enero del 2017

892 visualizaciones desde el 14 de Enero del 2017

161,2 KB

14 paginas

Creado hace 10a (05/05/2014)

Plataformas de Tiempo Real:

Dispositivos y Drivers

Tema 1. Arquitectura de E/S

• Aspectos básicos de la arquitectura de Entrada/Salida (E/S)

• Dispositivos e interfaces

• Buses

UNIVERSIDAD

DE CANTABRIA

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

8

© J. Javier Gutiérrez, Michael González

5/ma/14

1

Arquitectura básica de un computador

Un computador es una máquina que:

• acepta información de entrada

• la procesa ejecutando paso a paso una secuencia de

instrucciones o programa

UNIVERSIDAD

DE CANTABRIA

• y produce una información de salida.

El computador está por tanto compuesto por un equipo

electrónico (hardware) y un conjunto de programas (software)

El computador puede realizar dos tipos de instrucciones:

• acciones

• decisiones

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

2

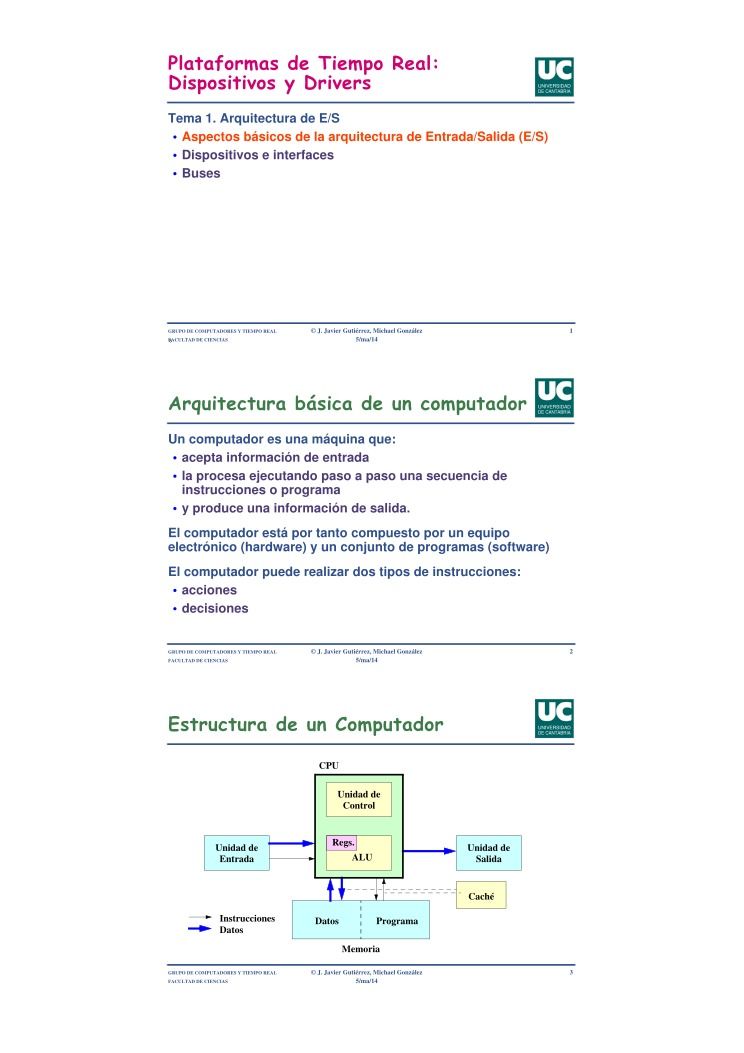

Estructura de un Computador

UNIVERSIDAD

DE CANTABRIA

CPU

Unidad de

Control

Regs.

ALU

Unidad de

Entrada

Instrucciones

Datos

Datos

Programa

Memoria

Unidad de

Salida

Caché

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

3

Rendimiento del computador

Las prestaciones de un computador no sólo dependen de la

velocidad del procesador, que en muchos de ellos es el

componente más rápido.

Los cuellos de botella están en:

• el intercambio de datos con la memoria:

UNIVERSIDAD

DE CANTABRIA

- se puede mejorar aumentando la anchura de los buses de datos, o

mediante los sistemas de memoria jerárquicos (cachés dentro y

fuera del procesador), o incluso mediante sistemas jerárquicos de

buses

• el intercambio de datos con los dispositivos de entrada/salida:

- puede llegar a ser importante en sistemas empotrados en los que

existe una fuerte interacción con el entorno y las operaciones de

entrada/salida son muy frecuentes

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

4

Plataformas de Tiempo Real:

Dispositivos y Drivers

Tema 1. Arquitectura de E/S

• Aspectos básicos de la arquitectura de Entrada/Salida (E/S)

• Dispositivos e interfaces

• Buses

UNIVERSIDAD

DE CANTABRIA

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

5

UNIVERSIDAD

DE CANTABRIA

Entrada y salida de datos

Los dispositivos de entrada/salida (E/S o I/O) forman junto con la

CPU y la memoria los elementos más importantes del computador

Uno de sus objetivos principales es la eficiencia en las

operaciones de entrada/salida, minimizando el trabajo a realizar

por la CPU

Las velocidades de los dispositivos de E/S son muy variadas:

• dispositivos lentos (p.e., ratón, teclado)

• dispositivos medios (p.e., impresora)

• dispositivos rápidos (p.e., red, disco)

Para acomodar las velocidades se usan circuitos de interfaz

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

6

Velocidades de dispositivos de E/S

UNIVERSIDAD

DE CANTABRIA

Dispositivos típicos de computadores

personales y estaciones de trabajo

Gigabit Ethernet

Gráficos

Disco duro

Ethernet

Disco óptico

Escáner

Impresora láser

Disquete

Módem

Ratón

Teclado

Velocidad de transferencia (bps)

= 109

< 6*108

< 108

= 107

< 107

< 5*106

< 2*106

< 106

< 105

< 2*102

< 102

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

7

Rendimiento y E/S

La generación actual de procesadores es capaz de manejar los

datos producidos por los dispositivos, pero el principal problema

está en la transferencia de datos entre el procesador y el periférico

Algunas soluciones están en:

• uso de cachés y almacenamientos intermedios

• buses de interconexión de mayor velocidad y con estructuras

UNIVERSIDAD

DE CANTABRIA

más elaboradas

• el uso de configuraciones multiprocesador puede ayudar

también a satisfacer altas demandas de E/S

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

8

Arquitectura de la E/S

UNIVERSIDAD

DE CANTABRIA

Unidad de

Control

CPU

Regs.

ALU

Regs.

Circuito de

Interfaz de

E/S

Datos

Programa

Memoria

Dispositivo

de E/S

Líneas de control

Líneas de direcciones

Líneas de datos

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

9

Arquitectura de la E/S (cont.)

Periférico:

• Dispositivo que permite al microprocesador su interacción con

UNIVERSIDAD

DE CANTABRIA

el entorno

Interfaz:

• Conjunto de módulos electrónicos que permiten el control de un

periférico adaptando las diferentes velocidades y modos de

funcionamiento del microprocesador y los periféricos

Bus:

• Normalmente se refiere al conjunto de señales con las que se

comunica el microprocesador con el entorno: memoria o

periféricos (a través de las interfaces)

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

10

Arquitectura de la E/S (cont.)

Las principales razones de uso de una interfaz son:

• Existen una gran variedad de periféricos con normas de

UNIVERSIDAD

DE CANTABRIA

funcionamiento diferentes y resultaría imposible implementar

en el procesador tal diversidad de controladores

• Las diferencias de velocidad de los dispositivos hace que no

sea práctico comunicarse con ellos directamente a través del

bus del sistema

• En algunos casos incluso la velocidad del dispositivo es mayor

que la de la memoria o el procesador

• Los periféricos utilizan datos con formatos y tamaños de

palabra diferentes de los del microprocesador al que se

conectan

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

11

Funciones de la interfaz de E/S

Control y temporización

• de la transferencia de datos entre el dispositivo y el procesador

• si el sistema utiliza un bus cada interacción de la interfaz de E/S

con el procesador puede requerir uno o más arbitrajes del bus

UNIVERSIDAD

DE CANTABRIA

Comunicación con el procesador

• decodificación de órdenes: la interfaz acepta órdenes del

procesador

• datos: intercambio de datos a través del bus

• información de estado: saber si el dispositivo está preparado

para transferir datos o no

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

12

Funciones de la interfaz de E/S

(cont.)

Comunicación con los dispositivos

• intercambio de órdenes, información de estado y datos

Almacenamiento temporal de datos

• fundamental para equilibrar las diferencias de velocidad del

procesador y de los periféricos

UNIVERSIDAD

DE CANTABRIA

• Ej.: el procesador puede enviar datos a ráfagas de la memoria a

un dispositivo que los procesa (de su almacén temporal) a una

velocidad varios órdenes de magnitud inferior

Detección de errores

• defectos mecánicos o eléctricos en el funcionamiento del

dispositivo (atasco de papel, cambio de un bit, etc.)

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

13

Conexión de las interfaces de E/S

Conexión mapeada en memoria

• el circuito de interfaz se conecta como si fuera memoria

• se accede a los registros leyendo o escribiendo una variable en

UNIVERSIDAD

DE CANTABRIA

una posición de memoria concreta

Conexión mediante puertos de entrada/salida

• el circuito de interfaz se conecta mediante líneas especiales

• se accede a los registros mediante instrucciones especiales (in,

out), especificando un número de puerto

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

14

Tipos de E/S

Entrada/salida por consulta o programada

• la CPU accede a los registros desde programa

• para saber si el dispositivo está listo, se hace una consulta

UNIVERSIDAD

DE CANTABRIA

periódica

Entrada/salida por interrupciones

• el dispositivo avisa a la CPU cuando está listo

• la entrada/salida se hace mediante una rutina de servicio de

interrupción

Entrada/salida por acceso directo a memoria

• el dispositivo accede directamente a la memoria

• avisa a la CPU del inicio o final de la operación

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

15

UNIVERSIDAD

DE CANTABRIA

a) E/S por consulta

La operación de E/S es controlada por la CPU

Antes de realizar la operación se comprueba el (los) registro(s) de

estado, para ver si el dispositivo está listo

Ventajas: sencillez

Desventajas:

• ritmo de transferencia limitado por la velocidad de la CPU

• tiempo de respuesta elevado, mayor que el periodo de consulta

• sobrecarga de la CPU para operaciones de consulta que podrían

evitarse

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

16

b) E/S por interrupciones

Permite al dispositivo marcar el instante en que se hace la

transferencia de datos

El mecanismo de interrupción está presente en casi todos los

computadores

UNIVERSIDAD

DE CANTABRIA

IRQ

IRQ

Mask

CPU

Unidad

de control

Regs.

Circuito de

Interfaz de

E/S

IACK

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

17

Identificación de la fuente de

interrupción

UNIVERSIDAD

DE CANTABRIA

CPU

CPU

IRQ

Por consulta

E/S-1

E/S-2

E/S-3

IRQ0

IRQ1

IRQ2

Por múltiples líneas

E/S-1

E/S-2

E/S-3

GRUPO DE COMPUTADORES Y TIEMPO REAL

FACULTAD DE CIENCIAS

© J. Javier Gutiérrez, Michael González

5/ma/14

18

Gestión de interrupciones

Las interrupciones se pueden enmascarar

• se utiliza para evitar la interrupción cuando se accede a datos

UNIVERSIDAD

DE CANTABRIA

compartidos con ella

Para cada interrupción se puede instalar una rutina de servicio de

interrupción

• al llegar la interrupción, el procesador interrumpe el programa

en ejecución y enmascara esa interrupción

• después ejecuta la ruti

Crear cuenta

Crear cuenta

Comentarios de: Plataformas de Tiempo Real: Dispositivos y Drivers - Tema 1. Arquitectura de E/S (0)

No hay comentarios