Lenguaje ABEL

l Introducción

l Estructura de un archivo fuente ABEL

o Formato

o Declaraciones

o Operadores

o Conjuntos

l Descripción lógica

o Ecuaciones

o Tablas

o Diagramas de estados

l Vectores de test

Introducción

l ABEL significa

o Advanced Boolean Equation Language

l Introducido por DATA I/O Corporation en 1984

o Diversos fabricantes lo siguen manteniendo

l Es un lenguaje de descripción de

hardware ...

…de bajo nivel

o Permite describir un circuito digital

o Permite definir vectores de test para

comprobar el funcionamiento

o Permite generar el mapa de fusibles

para programar el PLD

o Muy cercano a la circuitería

que representa

o Muy eficaz para describir

diseños digitales pequeños

(< algunos miles de puertas)

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 1

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 2

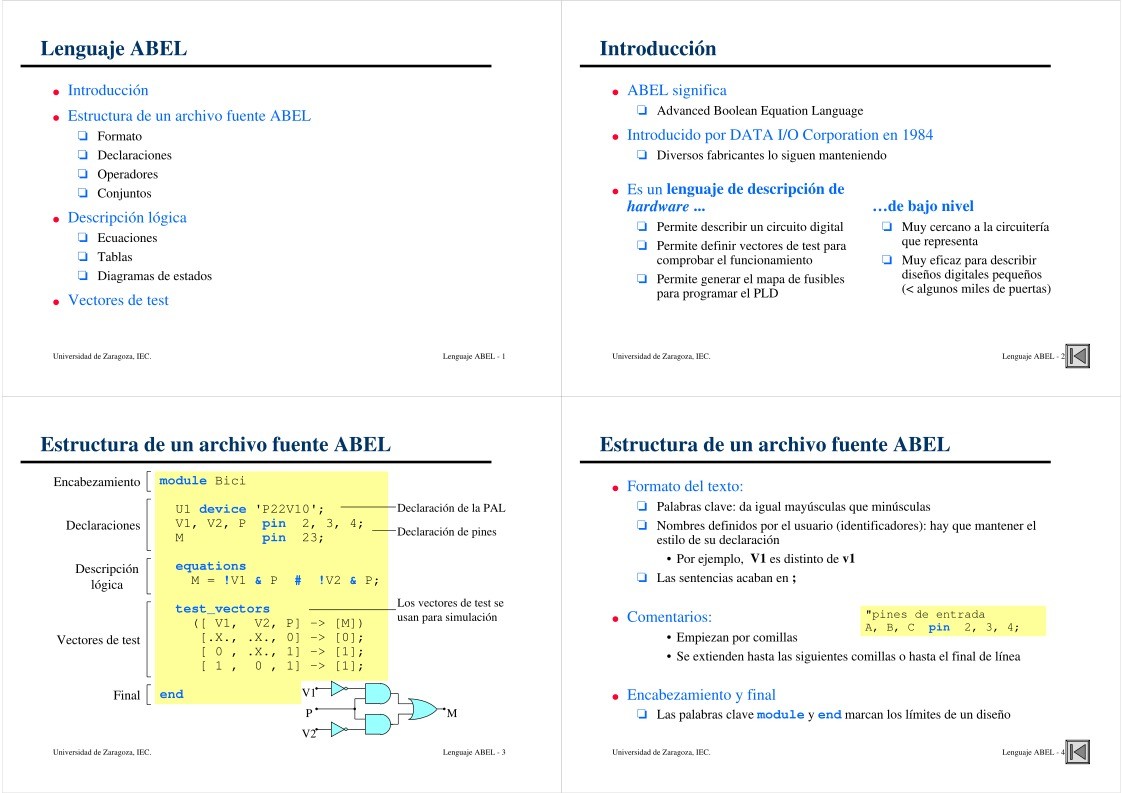

Estructura de un archivo fuente ABEL

Estructura de un archivo fuente ABEL

Encabezamiento

module Bici

Declaraciones

U1 device 'P22V10';

V1, V2, P pin 2, 3, 4;

M pin 23;

Declaración de la PAL

Declaración de pines

Descripción

lógica

equations

M = !V1 & P # !V2 & P;

Vectores de test

test_vectors

([ V1, V2, P] -> [M])

[.X., .X., 0] -> [0];

[ 0 , .X., 1] -> [1];

[ 1 , 0 , 1] -> [1];

Final

end

V1

P

V2

l Formato del texto:

o Palabras clave: da igual mayúsculas que minúsculas

o Nombres definidos por el usuario (identificadores): hay que mantener el

estilo de su declaración

• Por ejemplo, V1 es distinto de v1

o Las sentencias acaban en ;

Los vectores de test se

usan para simulación

l Comentarios:

• Empiezan por comillas

• Se extienden hasta las siguientes comillas o hasta el final de línea

"pines de entrada

A, B, C pin 2, 3, 4;

M

o Las palabras clave module y end marcan los límites de un diseño

l Encabezamiento y final

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 3

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 4

�Declaraciones

l Declaración del dispositivo

o Es opcional e identifica el PLD a usar

U1 device 'P22V10';

l Declaración de constantes

H, L = 1, 0;

Declaraciones

identificador device cadena

Cadena alfanumérica que

empieza por _ o una letra

Caracteres entre

comillas simples

l Declaración de pines

V1, V2, P pin 2, 3, 4;

id_pin1, id_pin2, ... pin nº_pin1, nº_pin2, ...

Lista de identif.

para los pines

Lista de

nº de pines (opcional)

l Declaración de señales internas

N1, N2, N3 node;

o En las arquitecturas tipo SPLD se asignan a un pin de salida (si no se pueden

simplificar en la síntesis)

id_cte1, id_cte2, ... = expr1, expr2, ...

Lista de identif.

para constantes

Lista de

expresiones

o Los números en ABEL siempre representan valores naturales

o Igual ocurre con los operadores aritméticos y relacionales

o La base por defecto es decimal

Base

Símbolo

Ejemplo: 17

en decimal

^b010001

^o21

^b

^o

Binaria

Octal

Decimal

Hexadecimal

^d (defecto)

^d17 o 17

^h

^h11

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 5

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 6

Operadores

l Lógicos

NOT (complemento a 1)

AND

OR

XOR

!

&

#

$

!$ XNOR

l Relacionales

o Comparan operandos en una

expresión

l Aritméticos

o Con conjuntos sólo - y +

Negación (compl. a 2)

Resta

Suma

-

-

+

<< Desplazamiento a izda.

>> Desplazamiento a dcha.

*

/

%

Multiplicación

División entera

Módulo (resto de A/B)

-A

A-B

A+B

A<<B

A>>B

A*B

A/B

A%B

o El resultado puede ser 1 (verdadero)

o 0 (falso)

l Asignación

Igual

Menor que

Mayor que

==

!= No igual

>

>= Mayor o igual que

<

<= Menor o igual que

Asignación combinacional

=

:= Asignación secuencial (en el

siguiente flanco de reloj)

A==B

A!=B

A>B

A>=B

A<B

A<=B

Conjuntos

l Lista de señales o constantes separadas por comas o por el operador

de rango (..), encerradas entre corchetes

o Simplifican la escritura de ecuaciones lógicas

o Declaración de conjuntos

ASET = [A2,A1,A0];

BSET = [Y2..Y0];

o Operaciones con conjuntos

• Se realizan sobre cada elemento del conjunto

• Los números se truncan o se rellenan con ceros

ASET & BSET

ASET & B0

2 & ASET

ASET = 2

[A2&B2, A1&B1, A0&B0]

[A2&B0, A1&B0, A0&B0]

[0&A2, 1&A1, 0&A0]

A2=0; A1=1; A0=0;

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 7

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 8

�Descripción lógica

Ecuaciones

l Se puede realizar de varias formas:

l Sentencias de asignación:

l El orden textual no importa

o Ecuaciones

• Palabra clave: equations

• Sentencia when-then-else

• Extensiones de punto

o Tablas

• Palabra clave: truth_table

o Diagrama de estados

• Palabra clave: state_diagram

• Sentencia if-then-else

• Sentencia goto

• Sentencia with-endwith

o Operador de asignación

combinacional (=)

equations

Y = A & B;

A

B

• Evitar realimentación

combinacional

equations

Y = Y & B;

B

o Operador de asignación

secuencial (:=)

equations

Y := A;

Y.clk = CK;

A

CK

equations

X := X+1;

Y := Y+X;

equations

Y := Y+X;

X := X+1;

[X,Y].clk = CK;

Y

Y

1

INCD.

X7..X0

Suma

Y7..Y0

D Q Y

CK

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 9

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 10

Ecuaciones

l Sentencia when-then-else

o Equivale a una ecuación

equations

when cond1 then

Y = exp1

else when cond2 then

Y = exp2

else

Y = exp3;

equations

Y = (cond1)&(exp1)

# !(cond1)& (cond2) &(exp2)

# !(cond1)& !(cond2)&(exp3);

D0

D1

D2

D3

00

01

10

11

Y

SEL=[S1,S0];

equations

when SEL==0 then Y=D0

else when SEL==1 then Y=D1

else when SEL==2 then Y=D2

else Y=D3;

S1 S0

Universidad de Zaragoza, IEC.

Extensiones de punto

l Se aplican a las salidas y permiten:

o Manejar señales especiales de la estructura de salida (OE, CLK; …)

o Eliminar ambigüedad en la descripción

l Las hay independientes del dispositivo (pin-to-pin) y dependientes

(detailed)

Independientes

Extensión

.oe

.clk

.aclr

.clr

.aset

.set

.fb

.pin

Descripción

Output enable

Reloj de biestable

Reset asíncrono

Reset síncrono

Preset asíncrono

Preset síncrono

Realim. Q de biestable

Realim. de la salida

Dependientes

Extensión

Descripción

.re

.ar

.sr

.pr

.ap

.sp

.d

.q

Reset

Reset asíncrono

Reset síncrono

Preset

Preset asíncrono

Preset síncrono

Entrada de biestable D

Realim. Q de biestable

Lenguaje ABEL - 11

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 12

�Extensiones de punto

Ejemplos

l Recomendable usar las extensiones independientes del dispositivo

o Se normalizan al pin de salida

l Ejemplos:

.set, .pr

.oe

.d

D

SPr

Q

.clk

ARe

.aclr, .re

.fb, .q

.pin

.clr, .pr

.oe

.d

D

SPr

Q

ARe

.aset, .re

.clk

.q

.fb

.pin

l Contador ascendente/descendente

módulo 8 con RESET asíncrono

l Contador módulo 13 con PRESET

síncrono y RESET asíncrono.

o Cuenta hacia arriba o hacia abajo,

según el valor de la entrada UP.

o La entrada de PRESET coloca al

contador a su valor máximo.

module Cont8

Cont8 device 'P22V10';

CLK,RST,UP pin 1,2,3;

Q2,Q1,Q0 pin 23,22,21;

CN = [Q2,Q1,Q0];

equations

when UP then CN:=CN+1

else CN:=CN-1;

CN.clk=CLK;

CN.aclr=RST;

end

module Cont13

Cont13 device 'P22V10';

CLK,RST,PRT pin 1,2,3;

Q3,Q2,Q1,Q0 pin 23,22,21,20;

CN = [Q3,Q2,Q1,Q0];

equations

when PRT then CN:=12

else when (CN==12) then CN:=0

else CN:=CN+1;

CN.clk=CLK;

CN.aclr=RST;

end

¡Ojo! Simulación de ecuaciones OK porque las salidas siempre están habilitadas

Para que la simulación sea OK indep. del PLD, realimentar con la extensión .fb

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 13

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 14

Realimentación en ecuaciones

Tablas

l Posibilidades:

o Sin extensión: Se realimenta del pin; si no existe, se realimenta del biestable

con polaridad normalizada al pin.

o Con .fb: Se realimenta del biestable con polaridad normalizada al pin; si no

existe, se realimenta del pin.

o Con .pin: Se realimenta del pin; si no existe resulta un error.

l Recomendable especificar de dónde se realimenta con .fb o .pin

o Resulta un diseño independiente del PLD

o La simulación de ecuaciones es igual que la simulación del JEDEC

• Si no ponemos extensión:

– Al compilar existen todos los caminos de realimentación <=> .pin

– Pero al encajar el diseño en una 22V10, se tiene en cuenta que la

realimentación es de biestable <=> .fb

Aparecen diferencias entre una simulación y otra

l Descripción tabular: salidas = f (combinaciones de entradas)

l Permite describir:

o Circuitos combinacionales

(tabla de verdad)

truth_table ([A,B] -> [Y])

[0,0] -> [0];

[0,1] -> [1];

[1,0] -> [1];

o Circuitos secuenciales (tabla de estados)

truth_table ([QB,QA] :> [QB,QA] -> [Y])

[0,0] :> [0,1] -> [0];

[0,1] :> [1,0] -> [0];

[1,0] :> [1,1] -> [0];

[1,1] :> [0,0] -> [1];

l El valor de la salida para combinaciones de entradas no

especificadas se toma como no importa

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 15

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 16

�Ejemplo de tabla

l Decodificador BCD a 7 segmentos

o Entradas: código BCD

o Salidas: visualizador de cátodo común

a

g

d

b

c

f

e

module BCD7

D3,D2,D1,D0 pin;

a,b,c,d,e,f,g pin;

BCD = [D3..D0];

ON,OFF = 1,0; "Invertir para ánodo común

truth_table(BCD ->[ a, b, c, d, e, f, g])

0 ->[ ON, ON, ON, ON, ON, ON,OFF];

1 ->[OFF, ON, ON,OFF,OFF,OFF,OFF];

...

9 ->[ ON, ON, ON, ON,OFF, ON, ON];

end BCD7

Diagramas de estados

l ABEL permite describir máquinas de estados (ME) introduciendo el

diagrama de estados

o Se realiza con la palabra clave state_diagram

l 4 Pasos en la descripción de una ME en ABEL:

o Definir las variables de estado.

o Definir/codificar los estados.

o Definir la función de transición de estados

• Sección state_diagram

o Definir la función de salida

• Sección state_diagram o equations

Universidad de Zaragoza, IEC.

Lenguaje ABEL - 17

Universidad de Zarago

Crear cuenta

Crear cuenta

Comentarios de: Lenguaje ABEL (0)

No hay comentarios