Publicado el 9 de Junio del 2020

1.952 visualizaciones desde el 9 de Junio del 2020

1,5 MB

35 paginas

Creado hace 17a (19/11/2007)

TD II - Microcontroladores ARM de 32 bits - 19/11/2007 - Ing. Susana Marta Canel A 1 -

1

Microcontroladores ARM

Advanced RISC Machine

Arquitectura ARM

Antecedentes

La arquitectura ARM se diseñó para permitir implementaciones de tamaño muy reducido

y de alto rendimiento. Estas arquitecturas tan simples permiten dispositivos con muy

bajo consumo de energía. Se caracteriza fundamentalmente por ser una computadora

de set de instrucciones reducido (Reduced Instruction Set Computer, RISC), como lo

indica su propio nombre.

El concepto RISC se originó en los programas de investigación de procesadores de las

universidades de Stanford y Berkeley, alrededor de 1980. El único ejemplo de

arquitectura RISC fue el de Berkeley, RISC I y II, y Stanford, MIPS (Microprocessor

without Interlocking Pipeline Stages).

El primer procesador ARM fue desarrollado, entre 1983 y 1985, por Acorn Computers

Limited of Cambridge, England. Fue el primer microprocesador RISC para uso

comercial. Las posteriores arquitecturas RISCs tuvieron diferencias significativas con

este primer diseño. Acorn tuvo una posición fuerte en el mercado de las computadoras

personales del Reino Unido debido al suceso de la microcomputadora BBC (British

Broadcasting Corporation). El micro BBC fue una máquina potenciada por un

microprocesador de 8 bits, el 6502.

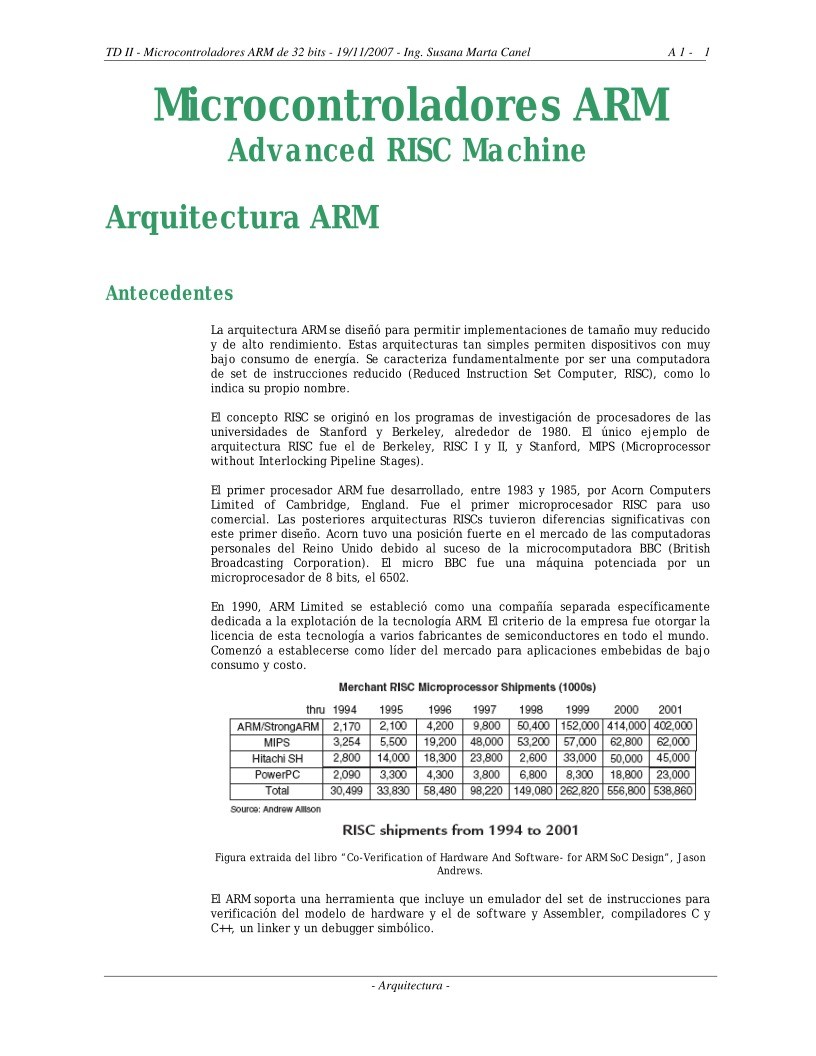

En 1990, ARM Limited se estableció como una compañía separada específicamente

dedicada a la explotación de la tecnología ARM. El criterio de la empresa fue otorgar la

licencia de esta tecnología a varios fabricantes de semiconductores en todo el mundo.

Comenzó a establecerse como líder del mercado para aplicaciones embebidas de bajo

consumo y costo.

Andrews.

Figura extraida del libro “Co-Verification of Hardware And Software- for ARM SoC Design”, Jason

El ARM soporta una herramienta que incluye un emulador del set de instrucciones para

verificación del modelo de hardware y el de software y Assembler, compiladores C y

C++, un linker y un debugger simbólico.

- Arquitectura -

�TD II - Microcontroladores ARM de 32 bits - 19/11/2007 - Ing. Susana Marta Canel A 1 -

2

Características heredadas de RISC

La arquitectura ARM incorporó algunas características del diseño RISC de

Berkeley, aunque no todas. Las que se mantuvieron son:

Arquitectura de carga y almacenamiento (load-store)

Las instrucciones que acceden a memoria están separadas de las

instrucciones que procesan los datos, ya que en este último caso los

datos necesariamente están en registros

Instrucciones de longitud fija de 32 bits

Campos de

simplificar la decodificación de las instrucciones.

instrucciones uniforme y de

longitud fija, para

Formatos de instrucción de 3 direcciones

Consta de “f” bits para el código de operación, “n” bits para

especificar la dirección del 1er. operando, “n” bits para especificar

la dirección del 2do. operando y “n” bits para especificar la

dirección del resultado (el destino). El formato de esta instrucción

en Assembler, por ejemplo para la instrucción de sumar dos

números para producir un resultado, es:

ADD d, s1, s2 ;d := s1 + s2

Figura 1.Formato de instrucción de tres direcciones.

En el formato de 3 direcciones de ARM las direcciones se especifican por

registros, que se han cargado previamente con el contenido de las

direcciones de memoria correspondientes.

En general, el término “arquitectura de 3 direcciones” se refiere a un

conjunto de instrucciones donde los dos operandos fuente y el destino, se

pueden identificar independientemente uno del otro, pero frecuentemente

solo dentro de un restringido conjunto de valores posibles.

Esta arquitectura no destructiva (el resultado de la operación no se escribe

sobre alguno de los operandos) permite a los compiladores organizar las

instrucciones de manera de optimizar el “pipeline”

(técnica de

procesamiento de varias instrucciones en “paralelo”)

- Arquitectura -

�TD II - Microcontroladores ARM de 32 bits - 19/11/2007 - Ing. Susana Marta Canel A 1 -

3

Características incorporadas por ARM

Características que posteriormente agregó ARM:

Todas las instrucciones se ejecutan en un ciclo de reloj

Modos de direccionamiento simples

El procesamiento de datos solo opera con contenidos de registros, no

directamente en memoria.

Control sobre la unidad aritmética lógica (ALU, Arithmetic Logic

Unit) y el “shifter”, en cada instrucción de procesamiento de datos

para maximizar el uso de la ALU y del “shifter”.

Modos de direccionamiento con

incremento y decremento

automático de punteros, para optimizar los lazos de los programas.

Carga y almacenamiento de múltiples instrucciones, para

maximizar el rendimiento de los datos.

Ejecución condicional de todas las instrucciones, para maximizar

el rendimiento de la ejecución.

Set de instrucciones ortogonal, regular o simétrico

En este tipo de set no hay restricciones en los registros usados en las

instrucciones, son todos registros de propósitos generales, con muy

pocas excepciones (por ejemplo el contador de programa, PC)

A los programadores Assembler les resulta más fácil aprender un set

con estas características. Y también, a los compiladores les resulta

más fácil manejarlo. Mientras que la implementación del hardware

será generalmente más eficiente.

Técnica “pipeline”

Esta técnica consiste en comenzar la próxima instrucción antes de

que la actual haya finalizado. El objetivo es economizar tiempo.

Excepciones vectorizadas

Las excepciones son condiciones inusuales o inválidas asociadas con

la ejecución de una instrucción particular.

Arquitectura “Thumb”

Algunos procesadores ARM tienen esta arquitectura para aplicaciones

que necesiten mejorar la densidad de código. Consiste en usar un set

de instrucciones de 16 bits que es una forma comprimida del set de

instrucciones ARM de 32 bits.

Estas mejoras sobre la arquitectura RISC básica permiten a los procesadores

ARM adquirir un buen equilibrio entre alto rendimiento, escaso tamaño de

código, bajo consumo y poca área de silicio.

- Arquitectura -

�TD II - Microcontroladores ARM de 32 bits - 19/11/2007 - Ing. Susana Marta Canel A 1 -

4

Revolución RISC

Reduced Instruction Set

Arquitectura RISC

En ese mundo de sets de instrucciones complejos en crecimiento, nació el

Reduced Instruction Set Computer (RISC). Este concepto fue el que más

influencia tuvo en el diseño de los procesadores ARM, inclusive ARM le debe

a RISC la letra del medio de su nombre.

Tamaño fijo de instrucciones de 32 bits, con pocos formatos

Arquitectura de almacenamiento y carga (load-store) donde las

instrucciones que procesan datos lo hacen solamente a través de

registros y separadas de las instrucciones que acceden a memoria.

Hay instrucciones para cargar los datos de memoria en registros y

otras para guardarlos desde registros a memoria.

Un banco grande de 32 registros. Todos ellos se pueden usar para

la arquitectura de

cualquier propósito, permitiendo que

almacenamiento y carga funcione eficientemente

Estas características simplifican enormemente el diseño del procesador y

permiten organizar la arquitectura de tal manera que aumenta el

rendimiento de los dispositivos.

Organización RISC

Lógica de decodificación de instrucción cableada por hardware.

Técnica de “pipeline”.

Tiempo de ejecución en un único ciclo. Los procesadores RISCs al

ser más simples se pueden diseñar para funcionar a velocidades de

reloj que pueden usar todo el ancho de banda disponible de las

memorias.

Ninguna de estas dos últimas propiedades es una característica de la

arquitectura, pero ambas dependen de la arquitectura, que es lo

suficientemente simple como para permitir que se las incorpore.

- Arquitectura -

�TD II - Microcontroladores ARM de 32 bits - 19/11/2007 - Ing. Susana Marta Canel A 1 -

5

Ventajas RISC

Menor desperdicio de área de silicio. Un procesador simple

economiza transistores y área de silicio. En consecuencia una CPU

RISC deja mayor área libre para realizar mejoras de rendimiento,

tales como, memoria caché, funciones de manejo de memoria,

punto flotante por hardware, etc.

Menor tiempo de desarrollo. Un procesador simple tiene menor

costo y lleva menos esfuerzo de diseño, además se adapta mejor a

los emprendimientos de tecnología de procesos.

Mayor rendimiento. Si se diseña un procesador simple y luego se le

agregan instrucciones complejas hará en forma más eficiente varias

funciones de alto nivel pero también decaerá un poco el reloj para

el conjunto de las instrucciones. Midiendo los beneficios de esta

técnica en programas típicos se comprueba que todos los sets de

instrucciones complejos hacen que el prog

Crear cuenta

Crear cuenta

Comentarios de: Microcontroladores ARM de 32 bits (0)

No hay comentarios