Actualizado el 21 de Marzo del 2018 (Publicado el 16 de Octubre del 2017)

1.384 visualizaciones desde el 16 de Octubre del 2017

751,8 KB

9 paginas

Creado hace 15a (01/06/2010)

COMENTARIO TECNICO

Microcontroladores de 32 bits ARM...

... O como no temerle al cambio!!

Por Ing. Marcelo E. Romeo1 - Ing. Eduardo A. Martínez2

Parte 1

1. Un poco de historia

1.1 Arquitectura RISC

En 1975, IBMiii se encontró con el requerimiento de Ericson de una central telefónica que

procesara 300 llamadas por segundo con un promedio de unas 20.000 instrucciones por

llamada, lo cual hacia necesario un procesador que realizara 12 millones de instrucciones

por segundo; en dicha época, ningún procesador de la época tenía esa potencia.

Un tiempo antes, se realizó un estudio estadístico de la frecuencia de ocurrencia de las

instrucciones sobre un programa generado por un compilador de alto nivel en una computadora

basada en un procesador de importantes prestaciones para la época.

Contrariamente a lo imaginado, la computadora realizaba mucho más frecuentemente

operaciones sencillas y muy esporádicamente operaciones complejas. El corolario fue que el

compilador no empleaba las instrucciones muy poderosas (que emplearía un programador en

assembler), sino que utilizaba instrucciones sencillas.

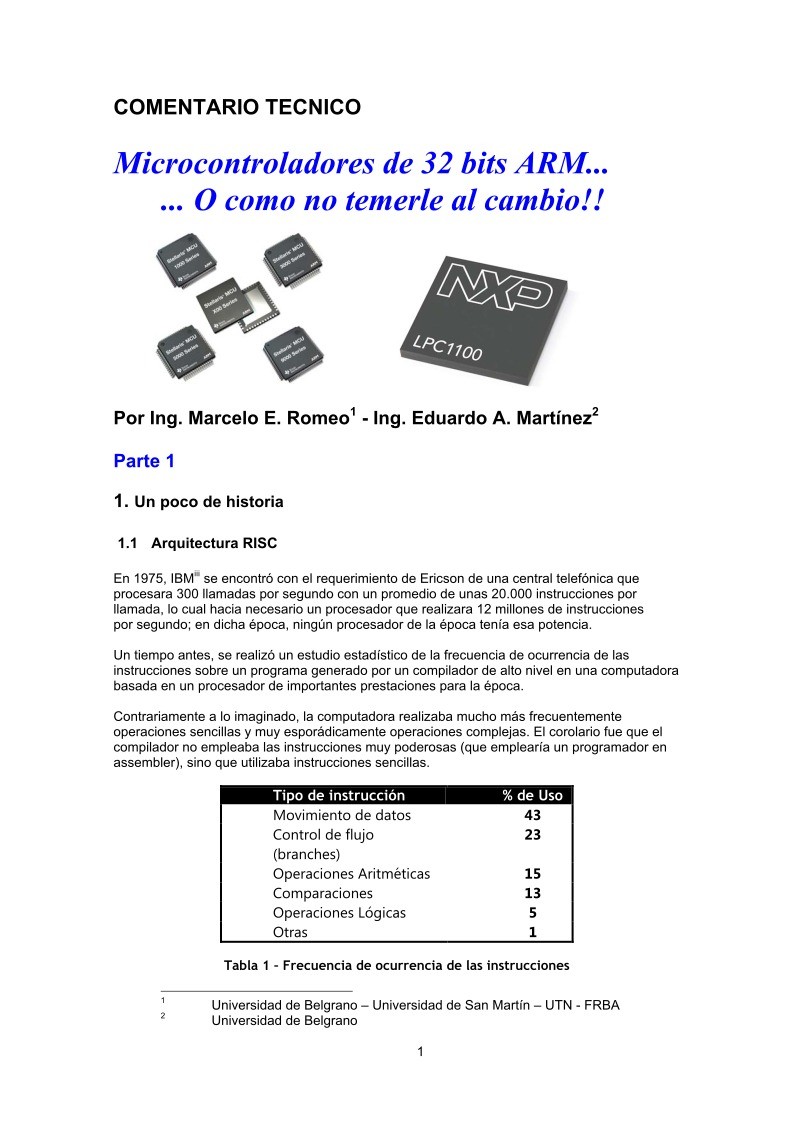

Tipo de instrucción

Movimiento de datos

Control de flujo

(branches)

Operaciones Aritméticas

Comparaciones

Operaciones Lógicas

Otras

% de Uso

43

23

15

13

5

1

Tabla 1 – Frecuencia de ocurrencia de las instrucciones

1

2

Universidad de Belgrano – Universidad de San Martín – UTN - FRBA

Universidad de Belgrano

1

�La central solicitada no requería muchas prestaciones y los cálculos que se requerían no eran

muy complejos, básicamente se necesitaba, añadir y mover datos y combinar campos.

Para resolver el requerimiento, IBM diseñó un procesador especial optimizando las

instrucciones más frecuentemente utilizadas y descartando las instrucciones complejas difíciles

de implementar en silicio y de uso poco frecuente. Las mismas deberían reemplazarse por

varias instrucciones sencillas pero muy rápidas.

Como suele ser frecuente, el proyecto no se cristalizó en un equipo comercial, pero dejó un

importante sedimento tecnológico: computadoras con una arquitectura de pocas instrucciones

pero muy veloces. Nació la arquitectura RISC (Reduced Instruction Set Computers).

El cambio laboral del diseñador Joel Birnbaum de IBM a HP y el nacimiento dentro de HP del

PA-RISC (Precision Architecture RISC o RISC de arquitectura precisa) conjuntamente con el

apoyo de las Universidades de Berkeley y Stanford a la investigación de RISC como

arquitectura por sus aplicaciones científicas y la energía puesta por HP por su comercialización

en el mercado de servidores, crearían la confianza suficiente en el mercado para la eclosión del

estándar.

Las principales características que comenzarían a hacer destacar a la arquitectura RISC

fueron:

Load / Store: Operaciones registro a registro separadas de los accesos a memoria.

•

• Repertorio de instrucciones cuidadosamente seleccionados, optimizados e

implementados en memoria

Instrucciones en formato fijo.

•

• Modos de direccionamiento simple

• Caches de instrucciones y datos separadas (Arquitectura Harvard)

• Paralelismo (Pipeline)

1.2 La familia de microcontroladores ARM

1.2.1 Orígenes y principios

En 1990, ARM una empresa surgida de Acorn Computers Limited of Cambridge, England,

diseñó el primer microcontrolador comercial de 32 bits de ancho de palabra basado en

arquitectura RISC3

El concepto tecnológico - comercial novedoso que implementaron fue la de diseñar el núcleo

de la familia de microcontroladores sin fabricarlos, sino que cedieron la producción a empresas

de semiconductores de primera línea (sólo como ejemplo, NXP, Atmel, Texas Instrumentes,

Freescale, Analog Devices, etc)4. Cada fabricante respetaría el núcleo original y el repertorio de

instrucciones, pero pudieron incorporarle sus propios periféricos (Conversores A/D y D/A,

UART, SPI, I2C, etc.), lo cual, por un lado, fue un estímulo al crecimiento de soluciones en

hardware, pero, sin embargo, produjeron incompatibilidades entre componentes similares de

distintas marcas.

3Acorn había hecho gran fama y fortuna al desarrollar una pequeña computadora de aplicaciones

estudiantiles y hobbistas en apoyo a programas didácticos presentados en la BBC de Londres.

4Una idea similar a la que tuvo Linus Torvalds con sus sistema operativo Linux

2

�1.2.2 Fuentes de la creación de la familia ARM

De la arquitectura RISC tomaron:

• Arquitectura load-store: Las instrucciones que acceden a memoria son distintas de

las instrucciones que procesan los datos

• Formato fijo de palabra de instrucción. Todas de 32 bits

• Máquina de tres direcciones (1er operando, 2º operando y resultado) en la que en la

instrucción se trabajará con registros punteros a operandos pero no directamente

con memoria

A su vez incorporaron algunos conceptos novedosos como ser:

• Ortogonalidad: Las instrucciones siguen un molde repetitivo. Por ejemplo la forma

de encarar la suma (operandos, formato), será la misma que para la OR exclusiva.

No existe registros especiales y esas operaciones pueden realizarse con todos los

registros.

•

Implementación de varios modos de trabajo o jerarquías. Aparece por primera

vez en un microcontrolador el modo supervisor y el modo usuario. El primero, con

plenos poderes, supervisará la actuación de los programas de usuario, impidiendo

que el sistema colapse y que solo pudieran hacerlo aplicaciones de usuario que

podrían ser rescatadas por el supervisor.

• Excepciones: Son los casos particulares de control de flujo (saltos) en los que un

efecto posiblemente no deseado de la ejecución del programa lleva a una situación

de falla, como un fallido acceso a memoria, un código de operación inválido, etc.,

llevan a que el programa se desvíe de su curso original y pase a ejecutar un tramo

de programa que atienda esta situación excepcional. Las interrupciones son un

caso particular de las excepciones.

• Thumb: Aparece la posibilidad de operar con códigos de operación comprimidos a

16 bits5. Si bien con ello parecería duplicarse el tamaño de la memoria de

programa, la realidad es que las instrucciones son menos poderosas que las de 32

bits, de forma que se requiere más de una instrucción de 16 bits para equiparar a

una de 32 bits.

• Bajo consumo: Se partió de la necesidad de bajo consumo, por lo que se bajó la

tensión de alimentación (1,8 V para el núcleo) y un interesante manejo de la

frecuencia de trabajo (ya que la potencia disipada es función directa de la

frecuencia) durante el tiempo de ejecución. Se llega a un consumo típico de 0,28

mW/MHz.

•

Interrupciones: Se dispondrá de dos interrupciones vectorizadas IRQ y FIQ las

cuales tendrán habilitaciones separadas y FIQ será de mayor prioridad que IRQ.

Se tomarán como casos particulares de excepciones.

• Eficiencia en la generación de código en C: Esta arquitectura fue concebida

para trabajar en lenguaje C con una densidad de código muy superior a los

microcontroladores de 8 bits previos en los que el lenguaje C apareció mucho

después del diseño del microcontrolador.

• Herramientas de depuración de bajo costo e incorporadas: Cada

microcontrolador dispone de una interfaz JTAG, originada para depurar DSPs y

que permiten generar herramientas de depuración en tiempo casi-real de muy bajo

costo.

5De la misma forma que la música en formato mp3 no mantiene la calidad de un CD original.

3

�2.

Características Básicas de la familia de procesadores ARM

2.1

Arquitectura

Fig 1: Arquitectura básica de un microcontrolador ARM7

En la figura 1 vemos a nivel de bloques elementales la arquitectura de un microcontrolador de

la familia ARM7. Observamos muchas coincidencias con las arquitecturas tradicionales de los

microcontroladores. Sin embargo debemos destacar algunas particularidades

• La totalidad de los registros son de 32 bits.

• La unidad aritmética lógica recibe uno de los operandos directamente del

banco de registros mientras que el otro operando pasa por un registro de

desplazamiento. Ese segundo operando podrá pasar transparentemente por

ese registro (sin verse afectado) o bien ser rotado a derecha o izquierda hasta

en 5 lugares, pudiendo multiplicarlo o dividirlo por 2n. Esas operaciones se

realizan en una sola instrucción y en un solo ciclo de máquina. Este pasaje por

el barrel shifter es similar al que se encuentra en los procesadores digitales de

señales (DSP) y que suele utilizarse para implementar filtros digitales. Aquí

también podremos implementar filtro digitales de buenas características hasta

el rango de audio.

• Decompresor Thumb. El procesador es único ya sea que se empleen códigos

de operación de 16 ó 32 bits. Cuando llegan los de 16 bits, automáticamente se

los expande a 32 bits (obviamente que con espacios rellenados por el propio

procesador) y se los ejecuta normalmente

4

�2.2

Modos de operación.

La familia introduce la novedad de disponer de siete modos distintos de operación.

• User: Modo NO privilegiado para la mayoría de las aplicaciones.

• FIQ: Se ingresa con una interrupción de alta prioridad (fast).

•

• Supervisor: Se ingresa en reset y cuando se ejecuta una interrupción por software

IRQ: Se ingresa con una interrupción de baja prioridad (normal).

que permitirá subir en nivel de jeraquías (SWI).

• Abort: Se emplea para gerenciar violaciones en el acceso a memoria.

• Undef: Se emplea para gerenciar instrucciones indefinidas.

• System: Modo privilegiado que emplea los mismos registros que el modo usuario

.

Esta asignación de modos de trabajo se ve acompañada con una disposición de registros que

permite un rápido cambio de contexto.

Inmediatamente después del reset, el procesador se inicia en modo Supervisor (donde tiene

todas las atribuciones). Realiza las inicializaciones y operaciones propias del modo y luego

cambia los bits de

Crear cuenta

Crear cuenta

Comentarios de: Microcontroladores de 32 bits ARM... ... O como no temerle al cambio!! (0)

No hay comentarios