Actualizado el 21 de Marzo del 2018 (Publicado el 15 de Diciembre del 2017)

2.057 visualizaciones desde el 15 de Diciembre del 2017

47,8 KB

12 paginas

Creado hace 22a (18/02/2003)

Universidad de Alcalá

Departamento de Automática

I. T. Informática de Sistemas

Laboratorio de Microprocesadores

INTRODUCCIÓN

El microprocesador de 16 bits 8086

En 1978 Intel sacó al mercado el 8086, con un bus de datos de 16 bits y capaz de

direccionar hasta 1 Mb de memoria. La importancia del 8086 se debe a que fue elegido por IBM

para desarrollar el Personal Computer, que fue tomado como estándar por casi todos los

fabricantes de ordenadores. Posteriormente Intel fabricó sucesivamente el 80186, el 80286, el

80386, el i486 y los Pentiums, manteniendo en todos ellos la compatibilidad software con los

anteriores.

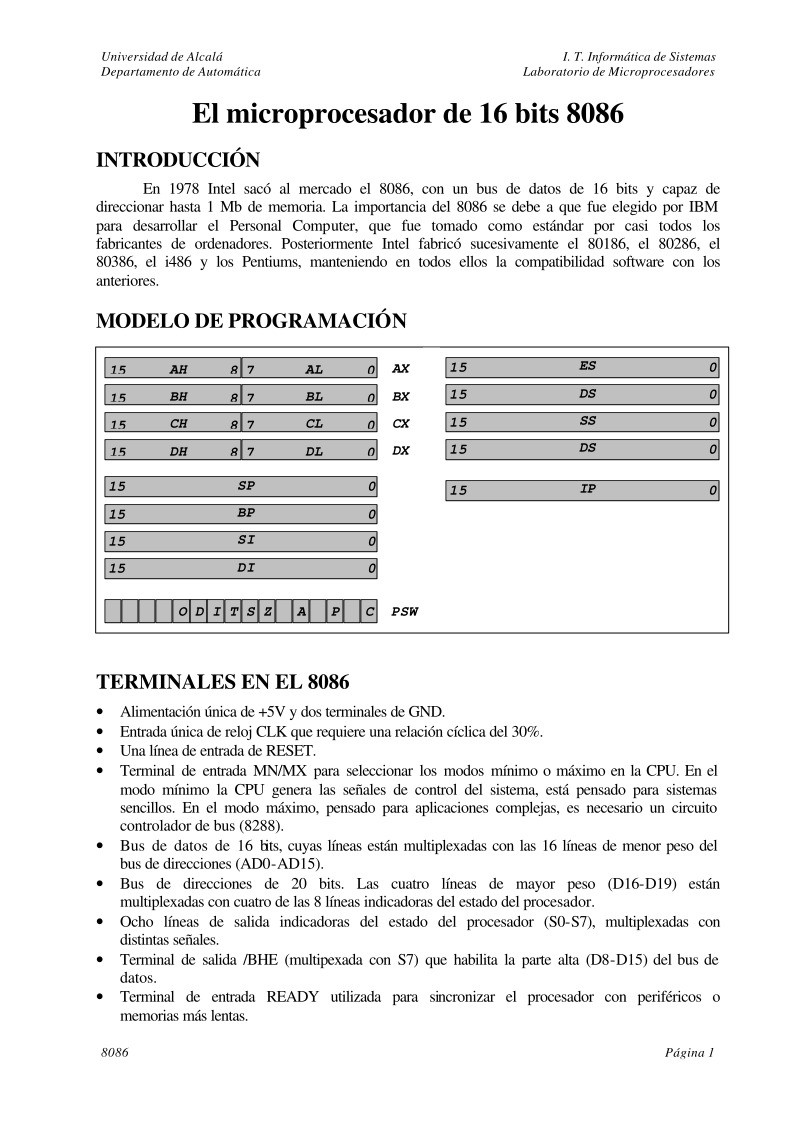

MODELO DE PROGRAMACIÓN

15 ES 0

15 DS 0

15 SS 0

15 DS 0

15 IP 0

15 AH 8

15 BH 8

15 CH 8

15 DH 8

7 AL 0

7 BL 0

7 CL 0

7 DL 0

AX

BX

CX

DX

15 SP 0

15 BP 0

15 SI 0

15 DI 0

O D I T S Z

A

P

C

PSW

TERMINALES EN EL 8086

• Alimentación única de +5V y dos terminales de GND.

• Entrada única de reloj CLK que requiere una relación cíclica del 30%.

• Una línea de entrada de RESET.

• Terminal de entrada MN/MX para seleccionar los modos mínimo o máximo en la CPU. En el

modo mínimo la CPU genera las señales de control del sistema, está pensado para sistemas

sencillos. En el modo máximo, pensado para aplicaciones complejas, es necesario un circuito

controlador de bus (8288).

• Bus de datos de 16 bits, cuyas líneas están multiplexadas con las 16 líneas de menor peso del

bus de direcciones (AD0-AD15).

• Bus de direcciones de 20 bits. Las cuatro líneas de mayor peso (D16-D19) están

multiplexadas con cuatro de las 8 líneas indicadoras del estado del procesador.

• Ocho líneas de salida indicadoras del estado del procesador (S0-S7), multiplexadas con

• Terminal de salida /BHE (multipexada con S7) que habilita la parte alta (D8-D15) del bus de

• Terminal de entrada READY utilizada para sincronizar el procesador con periféricos o

distintas señales.

datos.

memorias más lentas.

8086

Página 1

�Universidad de Alcalá

I. T. Informática de Sistemas

Departamento de Automática

Laboratorio de Microprocesadores

• Terminal de salida /RD para indicar operación de lectura y /WR para indicar operación de

escritura en memoria o puerto de entrada/salida.

para o no el procesador hasta una interrupción.

• Terminal de salida M/IO que indica si el acceso es a memoria o a un puerto.

• Terminal de entrada /TEST que es examinado en la instrucción WAIT para determinar si se

• Dos líneas de entrada de interrupciones: INTR (enmascarable) y NMI (no enmascarable).

• Línea de salida /INTA de reconocimiento de petición de interrupción enmascarable.

• Línea de salida ALE que indica dirección válida en el bus de direcciones/datos.

• Terminal de salida /DEN que valida el traspaso de datos en el bus de datos.

• Línea de salida DT/R que indica el sentido de la transferencia en el bus de datos.

• Terminal de entrada HOLD para que otro dispositivo tome el control del bus y terminal de

salida HLDA de cesión del citado bus.

• Terminales de salida que informan sobre el estado del procesador: S0-S2 indican la

operación que se está ejecutando, S3-S3 están multiplexadas con A16-A17 e indican el

registro de segmento que se está utilizando y S5 (multiplexada con A18) reproduce el flag I.

• Las señales RQ/GT0 RQ/GT1 permiten la comunicación con otros procesadores del mismo

bus local.

• La señal de salida /LOCK se activa con las instrucciones que incluyen el prefijo LOCK, para

indicar que no es posible la cesión del bus a ningún otro procesador.

• Las líneas QS0-QS1 informan sobre el estado de la cola interna de instrucciones.

Las señales M/IO, /WR, /INTA, ALE, DT/R, /DEN, HOLD y HLDA son exclusivas del

modo mínimo. Las señales S0-S2, RQ/GT0, RQ/GT1, /LOCK y QS0-QS1 solo están disponibles

en modo máximo

EL REGISTRO DE ESTADO (PSW)

• C (Carry) Flag de acarreo.

• P (Parity) Flag indicador de paridad.

• A (Auxiliar) Flag de acarreo auxiliar (del bit 3 al bit 4).

• Z (Zero) Flag indicador de cero.

• S (Sign) Flag indicador de signo del resultado.

• T (Trap) Flag indicador de ejecución paso a paso.

• I (Interrupt) Flag habilitación de interrupciones enmascarables.

• D (Direction) Flag de dirección ascendente/descendente en instrucciones de cadenas.

• O (Overflow) Flag indicador de desbordamiento.

INTERRUPCIONES

El 8086 puede tratar 256 tipos diferentes de interrupciones, que se numeran en

hexadecimal entre 0x00 y 0xFF y, según el modo en el que se producen, pueden ser internas

o externas. Las interrupciones externas son aquellas producidas por señales eléctricas

procedentes del exterior del microprocesador, normalmente producidas por los periféricos. Las

interrupciones internas son las producidas por la propia CPU en la ejecución de un programa

(por ejemplo ante el intento de división por cero) o por una instrucción específica (son las

interrupciones programadas que se producen cuando se ejecuta la instrucción INT).

Para poder realizar la gestión de todas las interrupciones, los primeros 1024 bytes de

memoria están reservadas para los vectores de interrupción que almacenan los valores que se

8086

Página 2

�

internas:

La propia CPU del 8086 es capaz de generar automáticamente tres interrupciones

• La interrupción 0 que se genera cuando se produce un intento de división por cero.

• La interrupción 1 que se genera después de ejecutarse cada instrucción si el flag T del

registro de estado está a 1, lo que permite la ejecución paso a paso y la depuración de

programas.

• La interrupción 4 es la interrupción de overflow y se genera cuando se produce una

Universidad de Alcalá

Departamento de Automática

I. T. Informática de Sistemas

Laboratorio de Microprocesadores

deben cargar en los registros IP y CS, para ejecutar la rutina de atención a la interrupción

correspondiente (la interrupción N tendrá su vector de interrupción a partir del byte de dirección

Nx4).

• La línea NMI, que provoca una interrupción no enmascarable que es atendida siempre

El 8086 dispone de dos líneas de petición de interrupción hardware:

mediante la rutina de vector 2.

• La línea INTR, que provoca una interrupción enmascarable, que solo será atendida si el

flag I está a 1, recibiendo en las 8 líneas de menor peso del bus de datos el número del

vector de interrupción. Esta línea es controlada por el circuito PIC (Programmable

Interrupt Controller) que se encarga también de situar el número de interrupción en el bus

de datos.

operación aritmética con desbordamiento.

Mediante la instrucción INT num se genera la interrupción representada por num, que

será atendida siempre, independientemente del estado del flag I.

ORGANIZACIÓN DE LA MEMORIA EN EL 8086

Aunque el 8086 dispone de 20 líneas en el bus de direcciones, la dirección de memoria se

obtiene a partir de dos registros de 16 bits mediante un sistema de segmentación de la memoria,

que equivale a subdividir la memoria en segmentos de 64 Kb, de modo que un registro de

segmento determina la dirección de comienzo de ese segmento de memoria y la posición relativa

(off-set o desplazamiento) la fija otro registro también de 16 bits. Así mediante la combinación

de ambos registros es posible direccionar cada una de las 65536 posiciones del segmento de 64

Kb.

Mediante la segmentación, los 5 dígitos hexadecimales necesarios para direccionar hasta

1 Mb, se obtienen desplazando un dígito a la izquierda el número representado en el registro de

segmento y sumándolo al número que representa el desplazamiento con respecto al origen, es

decir:

DIRECCIÓN FÍSICA = SEGMENTO * 16 + DESPLAZAMIENTO

Cuando se utiliza el método segmentado, las direcciones se expresan mediante el número

base y el offset o desplazamiento, ambos de 4 dígitos hexadecimales y separados por dos puntos.

Por ejemplo la dirección física 56F7A se puede representar escribiendo 56F7:000A ó

5000:6F7A ó 5600:0F7A, ... Con este procedimiento, toda la memoria puede dividirse en

segmentos, los cuales comienzan siempre en una dirección múltiplo de 16 y que, por supuesto,

pueden solaparse.

A la vista del su modelo de programación, el 8086 puede operar con datos de tipo byte y

de tipo palabra que se almacenan en memoria según el convenio de Intel, es decir, con la parte

8086

Página 3

�Universidad de Alcalá

Departamento de Automática

I. T. Informática de Sistemas

Laboratorio de Microprocesadores

menos significativa siempre en la dirección más baja, de modo que, por ejemplo, si suponemos

que AX=1234 y que TABLA representa a la dirección 100h (dentro del segmento de datos), la

instrucción MOV TABLA,AX hará que se almacene 34h en la dirección 100h y 12 en la 101h.

LENGUAJE ENSAMBLADOR DEL 8086

El ensamblador del 8086 establece para las líneas de programa la siguiente sintaxis:

Etiqueta: Código_de_Operación Operandos ;Comentarios

El

Crear cuenta

Crear cuenta

Comentarios de: El microprocesador de 16 bits 8086 (0)

No hay comentarios