Publicado el 14 de Enero del 2017

1.106 visualizaciones desde el 14 de Enero del 2017

632,2 KB

70 paginas

Capítulo 1 ● Introducción a los Computadores Paralelos

1 Introducción a los Computadores Paralelos

1. ¿Qué es la computación paralela?

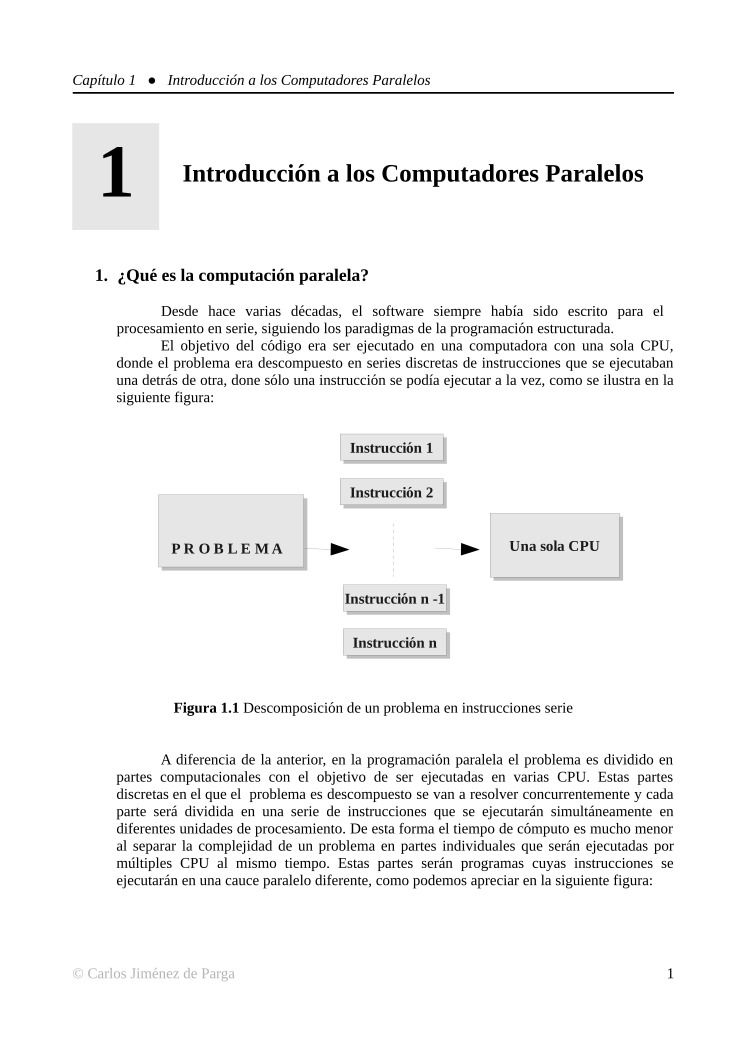

Desde hace varias décadas, el software siempre había sido escrito para el

procesamiento en serie, siguiendo los paradigmas de la programación estructurada.

El objetivo del código era ser ejecutado en una computadora con una sola CPU,

donde el problema era descompuesto en series discretas de instrucciones que se ejecutaban

una detrás de otra, done sólo una instrucción se podía ejecutar a la vez, como se ilustra en la

siguiente figura:

Instrucción 1

Instrucción 1

Instrucción 2

Instrucción 2

P R O B L E M A

Una sola CPU

Una sola CPU

Instrucción n -1

Instrucción n -1

Instrucción n

Instrucción n

Figura 1.1 Descomposición de un problema en instrucciones serie

A diferencia de la anterior, en la programación paralela el problema es dividido en

partes computacionales con el objetivo de ser ejecutadas en varias CPU. Estas partes

discretas en el que el problema es descompuesto se van a resolver concurrentemente y cada

parte será dividida en una serie de instrucciones que se ejecutarán simultáneamente en

diferentes unidades de procesamiento. De esta forma el tiempo de cómputo es mucho menor

al separar la complejidad de un problema en partes individuales que serán ejecutadas por

múltiples CPU al mismo tiempo. Estas partes serán programas cuyas instrucciones se

ejecutarán en una cauce paralelo diferente, como podemos apreciar en la siguiente figura:

© Carlos Jiménez de Parga

1

�Capítulo 1 ● Introducción a los Computadores Paralelos

P R O B L E M A

Instrucción 1

Instrucción 1

Instrucción 1

Instrucción 1

Instrucción 1

Instrucción 1

Instrucción 2

Instrucción 2

Instrucción 2

Instrucción 2

Instrucción 2

Instrucción 2

Instrucción n

Instrucción n

Instrucción n

Instrucción n

Instrucción n

Instrucción n

Instrucción n -1

Instrucción n -1

Instrucción n -1

Instrucción n -1

Instrucción n -1

Instrucción n -1

CPU 1

CPU 1

CPU 2

CPU 2

CPU 3

CPU 3

Figura 1.2 Ejecución paralela

2. Aplicaciones de la computación paralela

La computación paralela es una evolución de la computación serie que intenta

emular los aspectos del mundo real y natural: eventos complejos e interrelacionados

ocurriendo al mismo tiempo dentro de una secuencia. Así, tenemos la analogía de la

formación de galaxias, movimiento de planetas, patrones de eventos atmosféricos y de

océanos, movimiento de las placas tectónicas, control de tráfico, etc.

Históricamente la computación paralela se ha considerado el punto final de la más

alta computación y ha sido usada para resolver problemas complejos de ingeniería y ciencia

que acaecen en el mundo real.

2

�Capítulo 1 ● Introducción a los Computadores Paralelos

De esta forma encontramos el uso del paralelismo en computación en los siguientes

entornos:

• Cambio climático: Se están utilizando los patrones de cambios atmosféricos

para predecir con exactitud los fenómenos alterados del tiempo.

• Genoma: En el secuenciamiento de la estructura del ADN del código genético.

• Nanotecnología y química: Para crear nuevos compuestos moleculares con

propiedades microscópicas y materiales más resistentes a la fuerza y al calor.

• Geología y sismología: Utilizado en el estudio las propiedades geotécnicas y la

predicción de movimientos sísmicos.

•

Ingeniaría electrónica: Diseño de circuitos con más nivel de integración, más

rápidos y con menos calentamiento del chip.

• Prospección petrolífera: Debido al agotamiento de los combustibles fósiles se

ha hecho patente la necesidad de búsqueda de nuevos yacimientos para la

obtención de petróleo y gas.

• Buscadores Web: Con la proliferación incesante de Internet en la última década

se necesita una gran cantidad de recursos de cómputo que para rastrear e indexar

todos los contenidos publicados en la red.

• Diagnóstico por imagen: El avance de la medicina requiere de sistemas de

imagen capaces de diagnosticar con precisión y sin errores la existencia de

enfermedades.

•

Industria farmacéutica: En el diseño de nuevos medicamentos eficaces con los

mínimos efectos secundarios.

• Modelado económico y financiero: Las transacciones financieras realizadas en

un mundo globalizado pueden poner en riesgo la economía mundial. El análisis

complejo de estas interacciones de agentes puede prevenir una posible crisis

económica.

• Gráficos y realidad virtual: Con el fin de conseguir imágenes realistas en el

mundo de la infografía y los videojuegos.

© Carlos Jiménez de Parga

3

�Capítulo 1 ● Introducción a los Computadores Paralelos

3. Arquitecturas Von Neumann y secuenciales

El matemático húngaro John Von Neumann sentó las bases de la computación

moderna a la que pertenecen los ordenadores secuenciales, también denominados

computadores serie. Este modelo se basa en la Unidad Central de Procesamiento o CPU

(acrónimo anglosajón de Central Processing Unit), en la memoria donde se almacenan datos

e instrucciones. En esta arquitectura las instrucciones se ejecutan en serie que tratan con un

única secuencia de datos. En la sección 1.4 veremos más en profundidad los fundamentos

de este modelo.

M E M O R I A

M E M O R I A

Unidad de

Unidad de

Control

Control

ALU

Figura 1.3 Arquitectura Von Neumann (CPU y memoria)

Entrada

Entrada

Salida

Salida

Esta arquitectura presenta dos factores limitadores a tener en cuenta: la velocidad a la

que se ejecutan las instrucciones y la velocidad de transferencia de datos e instrucciones

entre la memoria y la CPU. En el primer factor están implicados los componentes y la

tecnología electrónica (frecuencia de reloj, etc.). No obstante, desde los años noventa se han

desarrollado nuevas estrategias para aumentar el rendimiento. La más conocida es la

segmentación que consiste en ejecutar varias partes de un número determinado de

instrucciones al mismo tiempo en varias unidades funcionales de cálculo (multiplicadores,

sumadores, unidades de carga y almacenamiento,...). Esto se consigue dividiendo las partes

de ejecución de una instrucción en etapas, alcanzando un rendimiento bastante mejorado con

respecto a una máquina no segmentada o secuencial. En la figura 1.4 podemos ver el

funcionamiento de una CPU segmentada.

Instrucción

i

i+1

i+2

i+3

i+4

Ciclo de reloj

1 2 3 4 5 6 7 8 9

IF ID EX MEM WB

IF ID EX MEM WB

IF ID EX MEM WB

IF ID EX MEM WB

IF ID EX MEM WB

Figura 1.4 Segmentación RISC

4

�Capítulo 1 ● Introducción a los Computadores Paralelos

Donde la etapa de ejecución IF es la búsqueda de instrucción en la caché o en la

memoria principal, ID es la decodificación de la instrucción y lectura de los registros, EX es

la etapa ejecución aritmético lógica, MEM es la lectura y escritura en memoria, y finalmente

WB escribe el resultado en los registros.

Como el lector puede apreciar, la ventaja de esta estrategia radica en que es posible

adelantar la ejecución de una instrucción en cada ciclo de reloj. En consecuencia en cada

ciclo de reloj se finaliza una instrucción y el incremento del rendimiento, sin tener en cuenta

los riesgos de la segmentación, es de un factor de cinco con respecto a una máquina que

ejecuta las instrucciones en serie.

En contraposición, aunque el incremento de la productividad es muy alto con

segmentación, el tiempo de CPU que se le dedica a una instrucción individual es superior al

de su homólogo secuencial. Esto es debido a:

• Los cerrojos que hay que colocar en la circuitería para separar la información

• La duración de las etapas es similar y viene determinada por la etapa más larga.

• Los riesgos estructurales, de datos y de control que introducen detenciones en el

entre etapas.

cauce de ejecución.

410 ns

410 ns.

410 ns.

80

80

80

Instrucción 1

90

80

80

90

80

80

Instrucción 2

90

80

90

80

80

Instrucción 3

80

95ns 95ns 95ns 95ns 95ns

Instrucción 1

Instrucción 2

Instrucción 3

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

Figura 1.5 Versión no segmentada (arriba) y segmentada de tres instrucciones (abajo)

5ns

© Carlos Jiménez de Parga

5

�Capítulo 1 ● Introducción a los Computadores Paralelos

Como puede observarse en la figura 1.5, la instrucción no segmentada consume 410

ns. , mientras que su equivalente segmentada consume 475 ns. , a causa de la etapa más lenta

que es 90 ns, en este caso suponiendo una segmentación ideal y un retardo de 5 ns. Por los

cerrojos de cada etapa segmentada. Esto implica un aumento de productividad que no

siempre está asociado a un incremento de velocidad de ejecución.

Con respecto a la segundo problema de la segmentación, éste admitiría dos

soluciones.

• Utilizar memoria entelazada o intercalada (memory interleaving):

Esta estrategia arquitectónica permite dividir la memoria en bloques, cada

uno con acceso independiente, tal y como puede verse en la siguiente figura:

Memoria 1

Memoria 1

CPUCPU

Memoria 2

Memoria 2

Memoria n

Memoria n

Figura 1.6 Memoria entrelazada

• Utilizar una memoria caché:

Otra estrategia más conocida para aumentar la velocidad de intercambio de

información es la memoria caché. Con esta memoria se consigue mayor velocidad de

intercambio en un e

Crear cuenta

Crear cuenta

Comentarios de: Tutorial CUDA (0)

No hay comentarios